Пространство адресов

ARMv7-M является системой с архитектурой отображаемой памяти.

Архитектура памяти ARMv7-M использует простое, плоское адресное пространство адресов из %% 2^{32} %% 8-битных байт. Байтовые адреса используются как беззнаковые целые начиная с %%0%% и заканчивая %%2^{32}-1%%.

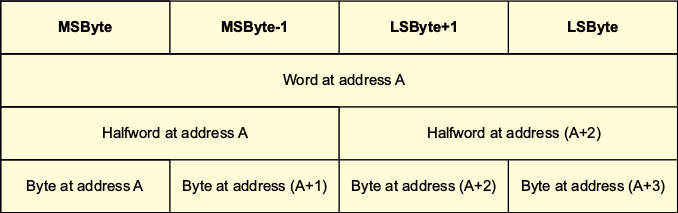

Это адресное пространство разбито на %%2^{30}%% 32-битных слов. Каждый такой адрес выровнен на размер слова. Это означает, что количество адресов разделёно на 4. Слово в таком выровненном на размер слова адресном пространстве, размещённое по гипотетическому адресу A состоит из четырёх байт с адресами A, A+1, A+2, A+3.

Всё адресное пространство также может быть интерпретировано как %%2^{31}%% 16-битовых полуслов. Выравнивание по размеру полуслова означает, что количество адресов разделяется на 2. Так, гипотетический адрес полусловно выровненного адреса A состоит из двух байт с адресами A и A+1.

В то время, как выборка инструкций всегда выровнена на полуслово (halfword), некоторые загрузки и выгрузки данных допускают невыровненные адреса.

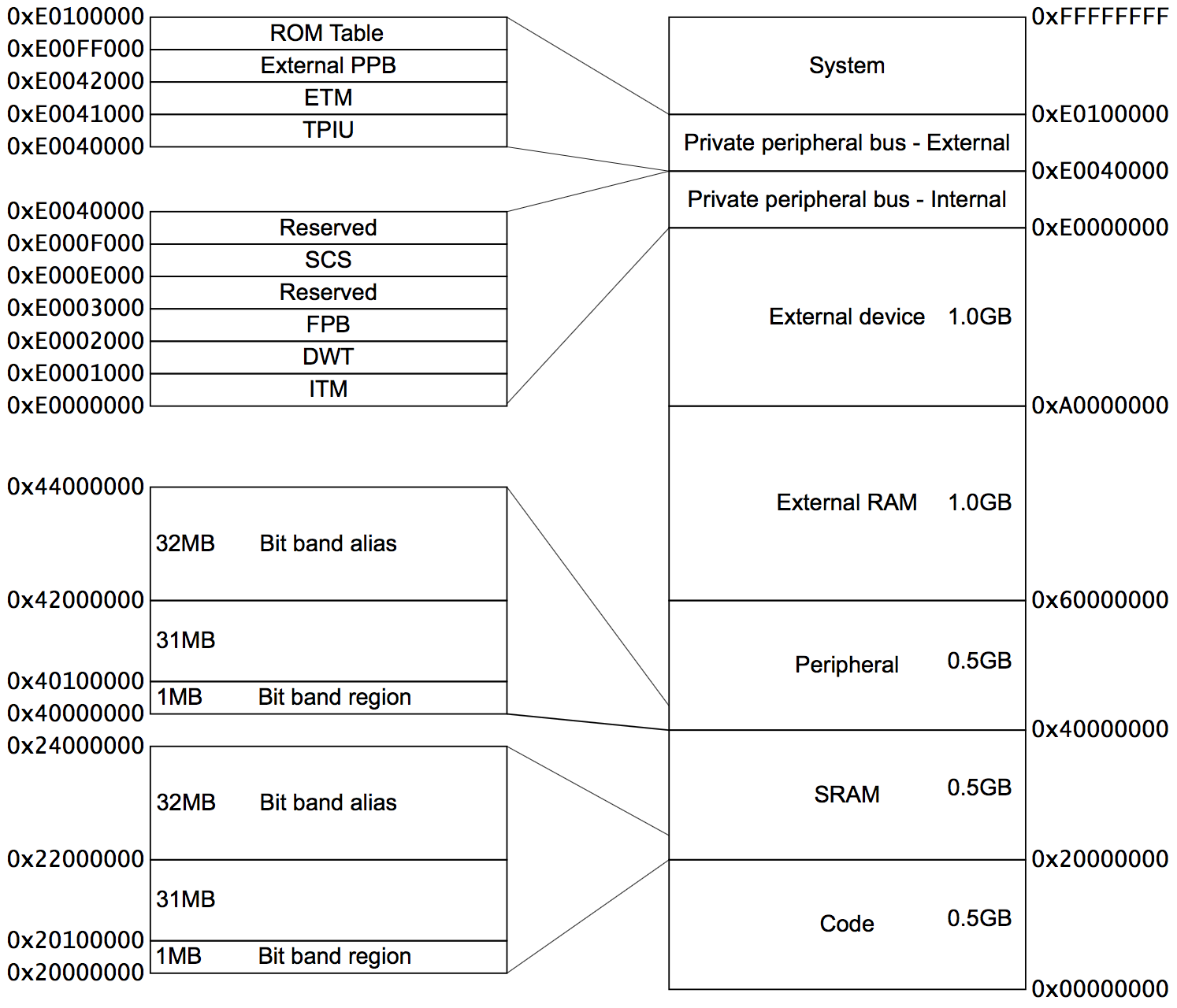

Карта памяти процессора Cortex-M3®:

Порядки следования байт

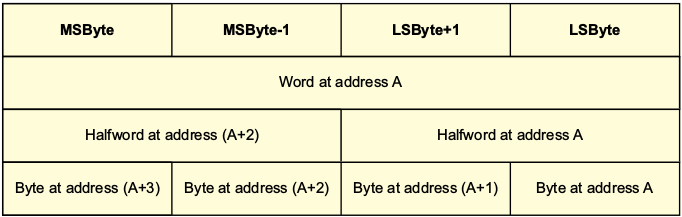

Правила организации адресного пространства для гипотетического адреса A:

- Слово(word) по адресу A состоит из байт по адресам A, A+1, A+2, A+3,

- Полуслово по адресу A состоит из двух байт по адресам A и A+1,

- Полуслово по адресу A+2 состоит из двух адресов A+2 и A+3,

- Слово по адресу A состоит из двух полуслов с адресами A и A+2

На самом деле это далеко не полностью описывает отображение между словами, полусловами и байтами. Во всех процессорах, при описании работы с памятью (или протоколами обмена) речь всегда идёт об использовани стандартизированной схемы отображения. Выбор конкретной схемы также известен как порядок порядок байт подсистемы памяти.

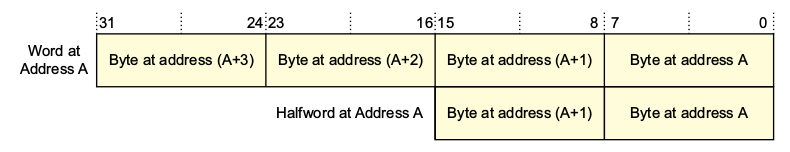

В little-endian (прямой порядок байт) системах, которая используется и в способах адресации в памяти и регистрах процессора ARM, байты адресуются следующим образом:

- байт (или полуслово) гипотетического адреса A является наименнее значимым в слове по этому адресу,

- байт в полуслове по гипотетическому адресу A является наименнее значимым в полуслове по этому адресу.

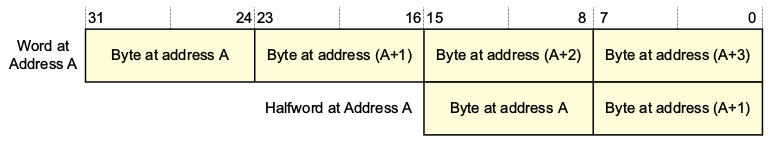

В big-endian системах (с обратным порядком следования байт) отображение между памятью и интерпретируемым в регистре процессора ARM осуществляется по следующей схеме:

- байт (или полуслово) гипотетического адреса A является наиболее значимым в слове по этому адресу,

- байт в полуслове по гипотетическому адресу A является наиболее значимым в полуслове по этому адресу.

Вот так будет выглядеть схема адресации в памяти с прямым порядком следования байт:

Little-endian подсистема памяти

и, соответственно, наоборот:

Big-endian подсистема памяти

Схемы прямого и обратного порядка адресации байт определяют способ интерпретации последовательности следования байт в слове и полуслове.

В качестве примера, загрузка слова (4 байта) из адреса 0x01000 всегда будет загрузкой 4 байт из адресов 0x01000, 0x01001, 0x01002 и0x01003 вне зависимости от используемого порядка следования байт. Порядок определяет лишь значение этого байта в рамках загруженного слова.

Контроль порядка в процессорах ARMv7

Архитектура ARMv7-M поддерживает определение используемой модели порядка следования байт на этапе сброса.

Выбираемый порядок имеет следующие подразумеваемые ограничения:

- Выбираемый порядок имеет значение только для операций с данными. Инструкции всегда загружаются в соответствии с прямым порядком.

- Любой доступ в пределах SCS всегда осущесвтляется в соответствии с прямым порядком.

Бит AIRCR.ENDIANNESS определяет порядок следования байт. Подробнее в разделе касающегося регистра контроля прерываний и сброса (AIRCR — Application Interrupt and Reset Control Register).

Реверс байт

Когда приложение, исполняющееся на процессоре или драйвер устройства имеют интерфейс с отображаемым на память периферийным регистром или разделяемой памятью с отличной от выбранной процессором последовательностью следования байт, наиболее эффективным путём работы с такими данными являются механизмы трансформации требуемых данных.

Процессоры ARMv7-M поддерживают следующие типы инструкций трансформаций:

REV— Реверс порядка следования байт слова (4 байта)REVSH— реверс порядка следования байт знакового полуслова.REV16— реверс порядка следования байт беззнакового полуслова.

| Функции | Интерфейсы |