Регистры процессора

Основные (core) регистры STM32F1xxx

Повествование содержит большое количество акронимов от названий регистров и др. В связи с тем, что акронимы часто уже содержат в своём имени слово регистр их использование должно предполагать отсутствие этого слова в предложении.

Однако, чтобы исключить неправильное толкование акронимов, составитель позволяет себе тавтологию в виде, например, регистр EPSR (вместо регистр EPS). Такое использование неправильно, но позволяет работать с акронимом EPSR и другими как с НАЗВАНИЯМИ.

Учитывая пользу от этого, автор будет считать использование акронимов как названий принятым в рамках курса соглашением.

Регистры общего назначения

R0-R12, которые традиционно делят на две группы:

R0-R7называются “нижними”R8-R12называются “верхними”

Указатель стека (Stack Pointer) SP

является тринадцатым R13 регистром.

Процессор поддерживает два стека (главный и программный, соответственно). Переключение между ними осуществляется манипуляцией соответствующего бита в регистре CONTROL.

Так, в режиме Thread Mode (и только в нём) бит[1] регистра CONTROL указывает, какой указатель используется конкретно. Всего может быть два варианта:

0= Main Stack Pointer (MSP). Основной указатель стека. Это значение принимается после сброса автоматически.1= Process Stack Pointer (PSP). Это значение может быть установлено принудительно при организации управления независимыми задачами.

В момент перезагрузки или сброса MSP автоматически получает значение 0x00000000.

LINK Регистр LP.

Link регистр это регистр R14. Это регистр специального назначения, предназнаенный для хранения информации об адресе возвращения, когда осуществляется вызов функции.

В отличии от универсального подхода в сохранении адреса возврата в стек, использование Link регистра является порой более эффективным, поскольку не осуществляется лишнее обращение к памяти.

Programm Counter (PC)

PC это регистр R15, который содержит текущий адрес выполняющейся программы. Бит[0] в этом регистре всегда 0, поскольку инструкции всегда должны быть выровнены по половине слова.

После перезагрузки или сброса процессор загружает в PC значение вектора прерывания сброса. Значение вектора находится по адресу 0x00000004.

Специальные регистры

Регистр состояния программы / Program Status Register (PSR)

Этот регистр комбинирует в себе несколько отдельных регистров:

- Application Programm Status Register

APSR— регистр состояния программы - Interrupt Programm Status Register

APSR— регистр состояния обработчика прерывания - Execution Programm Status Register

EPSR— регистр состояния исполнения

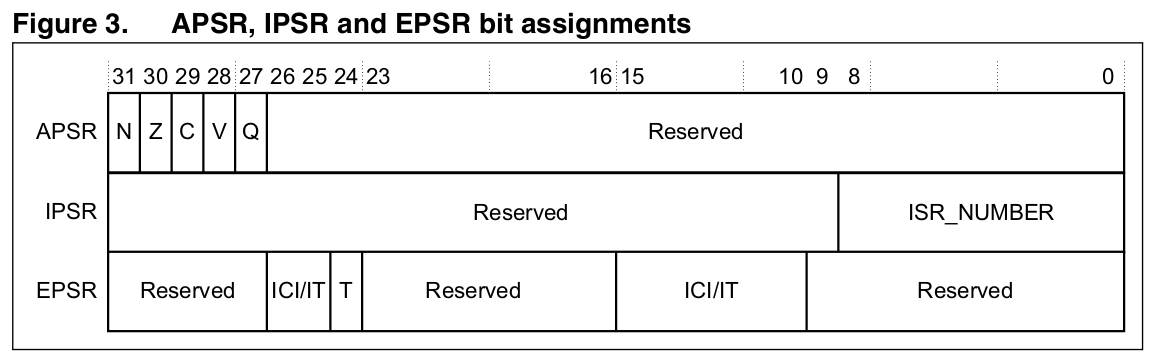

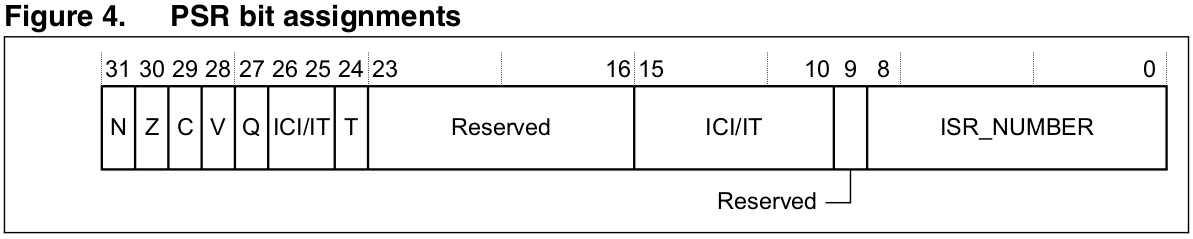

Эти регистры существуют в виде взаимоисключающих битовых полей в рамках 32-битного PSP. Назначение бит показано на рисунках Figure 3 и Figure 4 (STM32F10xxx Cortex-M3 programming manual):

Получить доступ к этим регистрам можно напрямую или как к комбинации двух или трёх регистров можно используя соотвествующее имя регистра как аргумент в MSR и MRS инструкциях. К примеру:

- Прочитайте все регистры с использованием

PSRвMRSинструкции; - Запишите в

APSRиспользуяAPSRвMSRинструкции.

Сочетания PSR в качестве атрибута следующее:

| Регистр | Доступ | Сочетания |

|---|---|---|

PSR | чтение/запись* | APSR, EPSR, IPSR |

IEPSR | только чтение | EPSR, IPSR |

IAPSR | чтение/запись** | APSR, IPSR |

EAPSR | чтение/запись*** | APSR, IPSR |

* — Процессор игнорирует запись в IPSR, чтение EPSR возвращает ноль и процессор игнорирует запись в этот регистр;

** — Процессор игнорирует запись в IPSR;

*** — Чтение EPSR возвращает нули в битах и процессор игнорирует попытки записи в этот регистр;

APSR Application programm status register

Регистр APSR содержит текущее состояние в виде флагов состояния, получившееся в результате выполнения предыдущей(последней) инструкции.

Биты распределены следующим образом:

- bit 31 | N | Флаг отрицания

0— Результат операции был позитивным или был равен нулю или в сравнении было больше или сравнение было равным1— Результат операции был отрицательным или результат сравнения был меньше- bit 30 | Z | Флаг нуля

0— Результат операции был НЕ равен нулю1— Результат операции был равен нулю.- bit 29 | C | Флаг переноса или заимствования

0— Результат операции сложения не привёл к выставлению бита как переноса или операция вычитания (соответственно) к выставлению бита как заимствования1— Результат операции сложения или вычитания привёл к выставлению бита как переноса или заимствования (соответственно).- bit 28 | V | Флаг переполнения

0— Операция не привела к переполнению1— Операция, соответственно, привела к переполнению- bit 27 | Q | “Липкий” флаг насыщения

0— Показывает, что насыщение не происходило с момента Reset или с момента, когда бит последний раз был принудительно сброшен в0. Обратите внимание, почему этот флаг “липкий”. Он не очищается автоматически в следующей команде.1— Показывает, чтоSSATилиUSATинструкции привели к насыщению. Этот бит сбрасывается программно с помощьюMSRинструкции.- bits 26:0 | Reserved

IPSR Interrupt program status register

Регистр IPSR содержит сведения о номере прерывания текущей процедуры обслуживания прерываний (ISR).

Биты распределены следующим образом:

- bits 31:9 | Reserved

- 8:0 | Номер прерывания

0— Thread mode1— Reserved2— NMI3— Hard fault4— Memory management fault5— Bus fault6— Usage fault7— Reserved- ...

10— Reserved11— SVCall12— Reserved for DEBUG13— Reserved14— PendSV15— SysTick16— IRQ0- ...

83— IRQ67

EPSR Execution program status register

Регистр EPSR содержит бит Thumb состояния и биты состояния выполнения для:

If-Then (IT)инструкций- Полем прерываемо-возобновляемой инструкции (

ICI) для инструкции прерываемой загрузки или сохранения множеств.

Биты распределяются так:

| Биты | Описание |

|---|---|

| bits 31:27 | Reserved |

| bits 26:25, 15:10 | ICI Interruptible-continuable instruction bits |

| bits 26:25, 15:10 | IT Показывает биты результата выполнения IT инструкции |

| bit 24 | всегда равен 1 |

| bits 23:16 | Reserved |

| bits 9:0 | Reserved |

Попытка чтения EPSR напрямую, с помощью программного вызова MRS инструкции всегда возращает ноль. Попытка записать ESPR напрямую будет проигнорирована. Обработчики ошибок могут изучить EPSR значение в составном PSR для указания какая операция привела к ошибке.

Interruptible-continuable instructions

Если прерывание происходит в процессе выполнения инструкций LDM или STM, процессор:

- Останавливает временно операцию загрузки или сохранения множества

- Сохраняет следующий регистровый операнд в множественной операции в биты регистра

EPSR[15:12]

После завершения обработки прерывания, процессор:

- Возвращает в регистр значение указанное в битах[15:12]

- Возобновляет выполнение множественной загрузки или выгрузки.

Когда EPSR удерживает ICI состояние выполнения биты [26:25, 11:10] всегда равны нулю.

If-Then block

If-Then блок содержит до 4-х инструкций, следующих за 16 битной IT инструкцией. Каждая инструкция в блоке является условной. Условия для инструкций либо одинаковые, либо некоторые могут быть инверсией остальных.

Exception mask registers / Регистры маскирования прерываний

Регистры маскирования прерываний запрещают обработку прерываний процессором. Запрет прерываний имеет большое влияние в вопросах критичных по времени выполнения операций.

Для доступа к регистрам маскирования прерываний использутся MSR и MRS инструкции или CPS инструкции для изменения значений PRIMASK или FAULTMASK.

Priority mask register / Регистр маски приоритетов

Регистр PRIMASK предотвращает срабатывание всех прерываний с конфигуририруемым приоритетом.

Регистр 32 битный. Биты с 31 по 1 зарезервированы, а нулевой бит работает так:

0— Нет эффекта1— Предотвращает срабатывание всех прерываний с конфигурируемым приоритетом.

Fault mask register

Регистр FAULTMASK предотвращает срабатывание любого прерывания за исключением немаскируемого прерывания NMI (Non-Maskable Interrupt).

В этом 32-битном регистре зарезервинрованы все биты с 31 по 1 и значимым является только нулевой бит.

Если он установлен в 0, то никакого эффекта это не имеет, если он имеет значение 1, то все вызовы прерываний, кроме NMI, предотвращены.

Процессор очищает FAULTMASK устанавливая нулевой бит в 0 на выходе из любого обработчика прерывания, кроме обработчика NMI.

Base priority mask register

Регистр BASEPRI определяет минимальный разрешённый приоритет для прерываний. Когда этот регистр установлен в ненулевое значение, это предотвращает срабатывание всех прерываний, с таким или более низким приоритетом, который указан в BASEPRI.

Регистр имеет зарезервированные биты [31:8] и [3:0]. Значимыми являются лишь биты [7:4]. Если в значимых битах записан 0x00, то никакого эффекта на работу процессора это не оказывает. Если там записано любое ненулевое значение, то определяет базовый приоритет для разрешённых обработчиков прерываний.

Учитывая, что нулевой приоритет самый высокий, ненулевое значение в этом регистре будет означать, что процессор НЕ будет обрабатывать любые прерывания, уровень приоритета которых БОЛЬШЕ ИЛИ РАВЕН значению в BASEPRI.

Регистр CONTROL

Регистр CONTROL управляет стэком и уровнем привелегий исполняемого ПО когда процессор находится в Thread режиме работы.

32-битный регистр имеет зарезервированными все биты [31:2], и активными [1:0].

Бит 1 имеет название ASPSEL и отвечает за то, какой указатель стека используется в настоящий момент:

- Значение

0означает, что используетсяMSP; - Значение

1означает, что используетсяPSP.

В режиме обработки прерываний (Handler Mode), бит всегда возвращает 0 и игнорирует попытки осуществить в него запись.

Бит 0 называется TPL и отвечает за установку уровня привелегий кода в Thread mode:

0— привелегированный код1— непривелегированный код.

Handler Mode всегда использует MSP, поэтому процессор игнорирует явные попытки записи в ASPSEL.

Если архитектура выполняемого ПО предполагает окружение операционной системы (OS), например, любую RTOS, то явной рекомендацией является использование MSP ядром и обработчиками прерываний, а PSP исполняемыми процессами.

По-умолчанию Thread Mode использует только MSP. Для переключения указателя в Thread mode на PSP следует использовать соответствующую MSR инструкцию.

Когда осуществляется смена указателя стека, ПО ДОЛЖНО вызвать ISB инструкцию непосредственно после MSR инструкции смены указателя. Это гарантирует, что инструкции после ISB будут использовать новый указатель стека.

| Буфер записи DCode и System шины | Simple quiz |