Функции

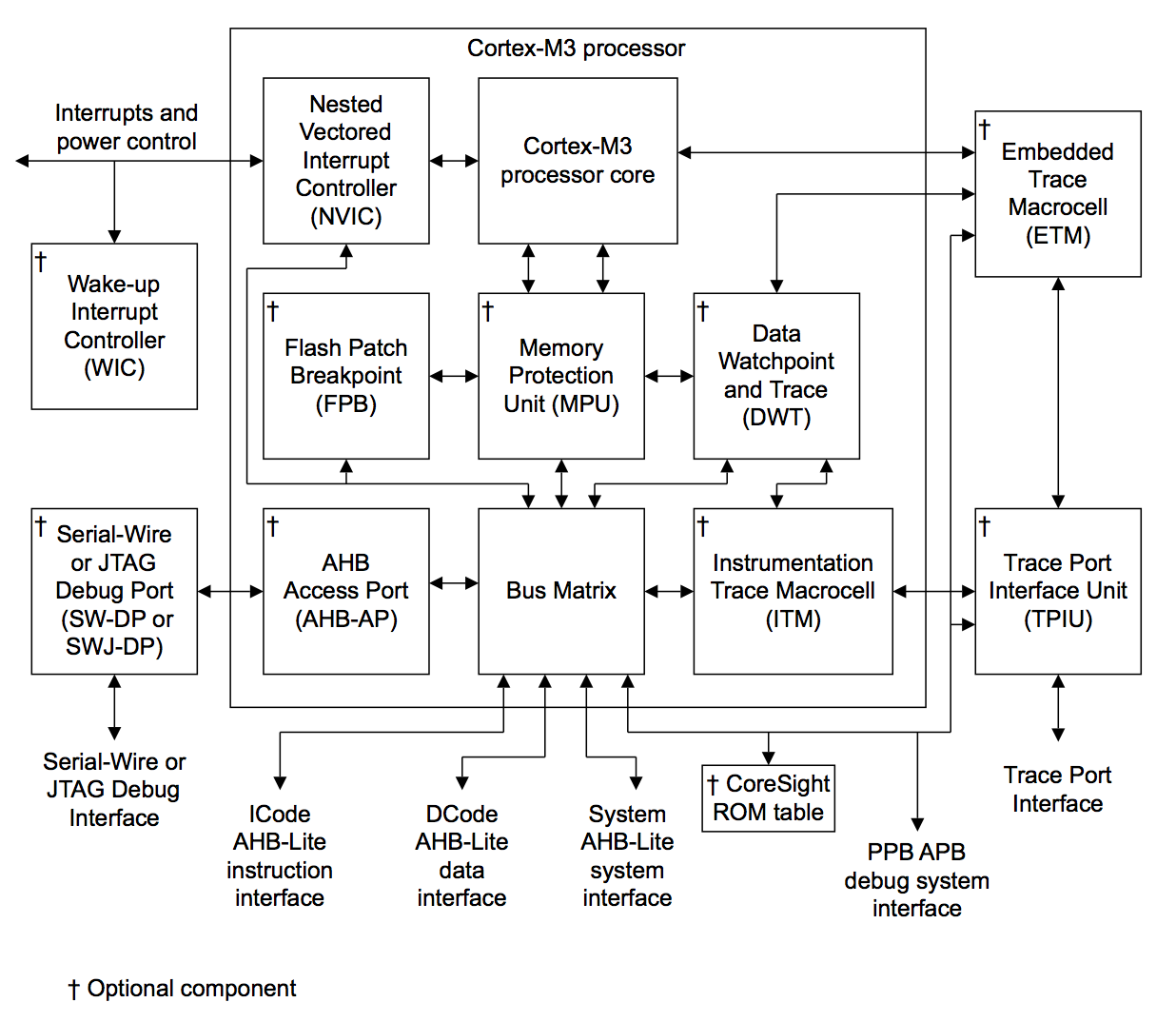

Изображение 2-1 показывает структуру процессора семейства Cortex M3®:

2-1. Блок-диаграмма процессора

Процессор имеет следующие функциональные преимущества:

Процессорное ядро, с механизмами поддержки ускоренной обработки прерываний, которое имеет:

- подмножество набора инструкций под названием Thumb, определённые в ARMv7-M Architecture Reference Manual;

- Переключаемый (banked) указатель стека (

SP); - Аппаратная поддержка операции деления с помощью команд

SDIVиUDIV; - Два режима исполнения кода: Handler и Thread;

- Подддерживаемые состояния Thumb и Отладка(Debug).

- Поддерживаемые прерываемо-продолжаемые инструкции

LDM,STM,PUSHиPOPс минимальными задержками исполнения; - Автоматическое сохранение и восстановление состояния процессора для быстрого входа и выхода из процедуры обслуживания прерываний (Interrupt Service Routine (

ISR); - Поддержка для ARMv6 big-endian порядка следования байт или для little-endian доступа к данным;

- Поддержка невыровненого доступа ARMv6.

Вкладываемый(комбинированный) векторизированный контроллер прерываний

NVIC, плотно итегрированный с процессорным ядром для снижения задержек при обработке прерываний:- Внешние прерывания, конфигурируемые по уровню от 1 до 240;

- Биты приоритетов, конфигурируемые от 3 до 8;

- Динамическая переприоретизация прерываний;

- Приоритетные группировки. Это позволяет определить уровни вытеснения и невытеснения прерываний;

- Поддержка сцепляющихся между собой прерываний и позднего срабатывания прерываний. Это позволяет обрабатывать прерывания идущие подряд без издержек на сохранение и восстановление состояния процессора между вызовами прерываний.

- Процессорное состояние сохраняется автоматически на входе в прерывание и автоматически восстанавливается на выходе без издержек на время выполнения дополнительных инструкций;

- Вспомогательный контроллер пробуждения (Wake-up Interrupt Controller (

WIC), предоставляющий возможность использовать режим сверхнизкого потребления электроэнергии.

Устройство защиты памяти (Memory Protection Unit (

MPU). Вспомогательный модуль MPU предоставляет:- Восемь отдельных областей памяти;

- Отключение по требованию области памяти (Sub Region Disable (

SRD) — свойство, позволяющее эффективно использовать под-области памяти; - Возможность включения фоновой области, делающее доступным реализацию функции карты памяти по-умолчанию.

Шинные интерфейсы:

- Три Продвинутых Высокопроизводительных Облегчённых шины (Advanced High-performance Bus-Lite (AHB-Lite):

ICode,DCode, иSystem bus; - Частная периферийная шина (Private Peripheral Bus (

PPB) основанная на интерфейсе Advanced Peripheral Bus (APB); - Разрядная (

Bit-band) технология доступа к памяти с поддержкой атомарных операций bit-band write и read. Это важная функция, позволяющая отразить отдельные биты периферии на байтовые адреса в памяти. Такой подход существенно упрощает разработку и переносимость программ; - Выравнивание доступа к памяти;

- Буферизацию для операций записи;

- Реализацию монопольного доступа для мультипроцессорных систем.

- Три Продвинутых Высокопроизводительных Облегчённых шины (Advanced High-performance Bus-Lite (AHB-Lite):

Поддержку технологий доступной и недорогой отладки:

- Отладочный доступ к любому участку памяти и регистру в системе, включая доступ к памяти сопоставленной устройствам (memory mapped devices), доступ к регистрам ядра процессора, когда ядро полностью остановленно и доступ к отладке контрольных регистров даже в случае когда получен сигнал SYSRESETn;

- Использование Последовательного Проводного Отладочного Порта (Serial Wire Debug Port (

SW-DP) или Последовательного Проводного Порта JTAG (SWJ-DP) или сразу оба этих порта; - Вспомогательный Flash Patch and Breakpoint (

FPB) модуль для реализации точек останова и накладывания патчей на исполняющийся код; - Вспомогательный Data Watchpoint and Trace (

DWT) модуль для реализации контрольных точек (watchpoints), трассировки данных (data tracing) и профилировки системы; - Вспомогательный Instrumentation Trace Macrocell (

ITM) для поддержки отладки в стиле printf; - Вспомогательный Trace Port Interface Unit (

TPIU) для переброски данных в Trace Port Analyzer (TPA), включая режим вывода отладочной информации по одному проводу (Single Wire Output (SWO). - Вспомогательный Embedded Trace Macrocell (ETM) для трассировки инструкций.

Совместимость процессора

Процессор реализует подмножество совместимых с другими семействами Cortex-M инструкций и функций. Вы можете перемещать своё программное обеспечение, включая системный уровень с Cortex-M3® на другие семейства.

Для обеспечения гладкого переноса, ARM рекомендует, чтобы разрабатываемый код не только на этой, но и на других Cortex-M процессоных архитектурах соответствовал следующим правилам и соответствующи образом сконфигурировал Configuration Control Register (CCR):

- используйте ТОЛЬКО перенос по словам для доступа к регистрав в

NVICи System Control Space (SCS). - обрабатывайте все неиспользуемые регистры и регистровые поля в процессоре в режиме “Не модифицировать” (Do-Not-Modify).

конфигурируется эти поля в регистре

CCR:STKALIGNбит в 1UNALIGN_TRPбит в 1- Оставьте все остальные биты в регистре

CCRв их оригинальных значениях.

| Функциональное описание | Пространство адресов |